Tradução: Maria Elisa - Assessoria em Inglês e Alemão

Revisão: Renato Kodaira

Circuitos especiais para lidar com as necessidades de aplicações em tempo real são o que separa um microcontrolador de outros processadores. A família dos microcontroladores PIC16F627A, PIC16F628A e PIC16F648A possui uma série de características específicas que visam maximizar a confiabilidade do sistema, minimizar o custo através da eliminação de componentes externos, prover modos de operação com economia de energia e oferecer proteção de código.

Estas são:

-

Seleção OSC

-

Reinicialização

-

Reinicialização de Power-on (POR)

-

Temporizador de Ativação (PWRT)

-

Temporizador de Inicialização do Oscilador (OST)

-

Reinicialização de Brown-out (BOR)

-

Interrupções

-

Temporizador Cão-de-Guarda

-

Hibernação

-

Proteção de código

-

Posições de ID

-

Programação Serial In-CircuitTM (ICSPTM)

Os microcontroladores PIC16F627A, PIC16F628A e PIC16F648A possuem um Temporizador Cão-de-Guarda que é controlado por bits de configuração. Ele conta com seu próprio oscilador RC, proporcionando confiabilidade adicional. Existem dois temporizadores que oferecem os delays necessários na ativação. Um deles é o Temporizador de Inicialização do Oscilador (OST), que visa manter o chip na Reinicialização até que o oscilador de cristal esteja estável. O outro é o Temporizador de Ativação (PWRT), o qual provê um delay fixo de 72ms (nominal) somente na ativação, designado a manter o dispositivo em Reinicialização enquanto o fornecimento de energia se estabiliza. Também existem circuitos para reiniciar o dispositivo caso ocorra um brown-out. Com estas três funções on-chip, a maioria das aplicações não necessita de circuitos externos de Reinicialização.

O modo de Hibernação visa oferecer um desligamento com corrente muito baixa. O usuário pode acordar o dispositivo da Hibernação através da Reinicialização externa, do Temporizador Cão-de-Guarda ou de uma interrupção. Várias opções de osciladores também são disponibilizadas para permitir o dispositivo se adequar à aplicação. A opção do oscilador RC reduz o custo do sistema, enquanto a opção do cristal LP economiza energia. Uma série de bits de configuração são utilizados para selecionar as várias opções.

Os bits de configuração podem ser programados (lidos como '0') ou deixados sem programação (lidos como '1'), a fim de selecionar diversas configurações do dispositivo. Estes bits estão mapeados na posição 2007h da memória de programa.

O usuário perceberá que o endereço 2007h está situado no espaço da memória do programa destinado ao usuário. De fato, ele pertence ao espaço da memória especial para configuração (2000h - 3FFFh), que pode ser acessado somente durante a programação. Veja a "Especificação de Programação da Memória EEPROM dos PIC16F627A/628A/648A" (DS41196) para informações adicionais.

REGISTRADOR 14.1: CONFIG - REGISTRADOR DA PALAVRA DE CONFIGURAÇÃO

|

|

|

CP |

--- |

--- |

--- |

--- |

CPD |

LVP |

BOREN |

MCLRE |

FOSC2 |

PWRTE |

WDTE |

FOSC1 |

FOSC0 |

|

bit 13 |

|

|

|

|

|

|

|

|

|

|

|

|

bit 0 |

|

|

bit 13 |

CP: Bit de Proteção de Código da Memória Flash de Programação(2) |

|

|

(PIC16F648A) |

|

|

1 = Proteção de código desativada |

|

|

0 = código protegido de 0000h até 0FFFh |

|

|

(PIC16F628A) |

|

|

1 = Proteção de código desativada |

|

|

0 = código protegido de 0000h até 07FFh |

|

|

(PIC16F627A) |

|

|

1 = Proteção de código desativada |

|

|

0 = código protegido de 0000h até 03FFh

|

bit 12-9

|

Não Implementados: Lidos como '0'

|

|

bit 8 |

CPD: Bit de Proteção de Código da Memória de Dados(3) |

|

|

1 = Proteção de código da memória de dados desativada |

|

|

0 = Memória de dados protegida

|

|

bit 7 |

LVP: Bit de Habilitação da Programação em Baixa tensão |

|

|

1 = O pino RB4/PGM possui a função PGM, programação em baixa tensão habilitada. |

|

|

0 = O RB4/PGM é uma entrada/saída digital, deve ser utilizada alta tensão em MCLR para a programação.

|

|

bit 6 |

BOREN: Bit de Habilitação da Reinicialização de Brown-out(1) |

|

|

1 = Reinicialização BOR habilitada |

|

|

0 = Reinicialização BOR inabilitada

|

|

bit 5 |

MCLRE: Bit de Seleção da Função do Pino RA5/MCLR/VPP |

|

|

1 = A função do pino RA5/MCLR/VPP é MCLR |

|

|

0 = A função do pino RA5/MCLR/VPP é de entrada digital, MCLR ligado internamente à VDD

|

|

bit 3 |

PWRTE: Bit de Habilitação do Temporizador de Ativação(1) |

|

|

1 = PWRT desabilitado |

|

|

0 = PWRT habilitado

|

|

bit 2 |

WDTE: Bit de Habilitação do Temporizador Cão-de-Guarda |

|

|

1 = WDT habilitado |

|

|

0 = WDT desabilitado

|

|

bit 4, 1-0 |

FOSC<2:0>:Bits de Seleção do Oscilador(4) |

|

|

111 = Oscilador RC: Função CLKOUT no pino RA6/OSC2/CLKOUT, Resistor e Capacitor no RA7/OSC1/CLKIN |

|

|

110 = Oscilador RC: Função I/O no pino RA6/OSC2/CLKOUT, Resistor e Capacitor no RA7/OSC1/CLKIN |

|

|

101 = Oscilador INTOSC: Função CLKOUT no pino RA6/OSC2/CLKOUT, função I/O no RA7/OSC1/CLKIN |

|

|

100 = Oscilador INTOSC: Função I/O no pino RA6/OSC2/CLKOUT, função I/O no RA7/OSC1/CLKIN |

|

|

011 = EC: Função I/O no pino RA6/OSC2/CLKOUT, CLKIN no RA7/OSC1/CLKIN |

|

|

010 = Oscilador HS: Cristal/ressonador de alta velocidade no RA6/OSC2/CLKOUT e no RA7/OSC1/CLKIN |

|

|

001 = Oscilador XT: Cristal/ressonador no RA6/OSC2/CLKOUT e no RA7/OSC1/CLKIN |

|

|

000 = Oscilador LP: Cristal de baixa corrente no RA6/OSC2/CLKOUT e no RA7/OSC1/CLKIN |

|

|

Notas: |

|

|

1: A habilitação da Reinicialização de Brown-out não habilita automaticamente o Temporizador de Ativação (PWRT), como ocorre nos dispositivos PIC16F627/628. |

|

|

2: O esquema de proteção de código foi alterado em relação ao utilizado nos dispositivos PIC16F627/628. É necessário que a memória Flash de programação seja completamente apagada para se ativar o bit CP, desativando a proteção de código. Veja a "Especificação de Programação da Memória EEPROM dos PIC16F627A/628A/648A" (DS41196) para detalhes. |

|

|

3: É necessário que a memória de dados EEPROM seja completamente apagada para se ativar o bit CPD, desativando a proteção de código. Veja a "Especificação de Programação da Memória EEPROM dos PIC16F627A/628A/648A" (DS41196) para detalhes. |

|

|

4: Quando o MCLR estiver no modo INTOSC, o oscilador do clock interno está desabilitado.

|

|

|

Legenda:

R = bit de leitura

W = bit de escrita

U = bit não implementado (unimplemented), lido como '0'

-n = valor na POR

'1' = bit está ativado

'0' = bit está apagado

x = bit é desconhecido |

14.2 Configurações do Oscilador

14.2.1 TIPOS DE OSCILADOR

Os microcontroladores PIC16F627A, PIC16F628A e PIC16F648A podem ser operados em oito diferentes opções de oscilador. O usuário pode programar três bits de configuração (FOSC2 até FOSC0) para selecionar um destes oito modos:

-

LP: Cristal de Baixa Corrente

-

XT: Cristal/Ressonador

-

HS: Cristal/Ressonador de Alta Velocidade

-

RC: Resistor/Capacitor externo (2 modos)

-

INTOSC: Oscilador de Precisão interno (2 modos)

-

EC: Clock Externo Disponível

14.2.2 OSCILADOR DE CRISTAL/RESSONADORES CERÂMICOS

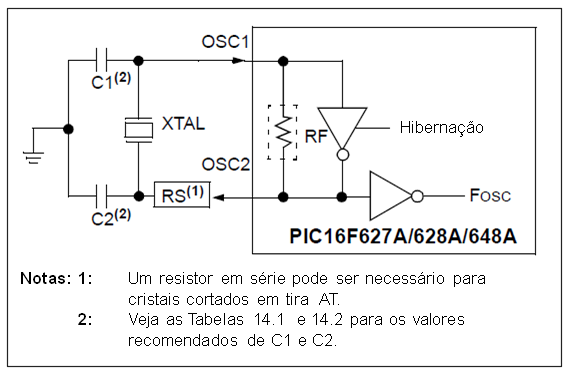

Nos modos XT, LP ou HS, um cristal ou ressonador cerâmico é conectado aos pinos OSC1 e OSC2 para estabelecer a oscilação (Figura 14.1). O design do oscilador dos PIC16F627A/628A/648A requer o uso de um cristal de corte paralelo. A utilização de um cristal de corte em série pode proporcionar uma frequência fora das especificações do fabricante do cristal. Quando nos modos XT, LP ou HS, o dispositivo pode ter uma fonte de clock externa para conduzir o pino OSC1 (Figura 14.4).

TABELA 14.1: SELEÇÃO DO CAPACITOR PARA RESSONADORES DE CERÂMICA

|

Modo |

Freq |

OSC1 (C1) |

OSC2 (C2) |

|

XT |

455 kHz |

22 - 100 pF |

22 - 100 pF |

|

2.0 MHz |

15 - 68 pF |

15 - 68 pF |

|

4.0 MHz |

15 - 68 pF |

15 - 68 pF |

|

HS |

8.0 MHz |

10 - 68 pF |

10 - 68 pF |

|

16.0 MHz |

10 - 22 pF |

10 - 22 pF |

Nota:

Uma capacitância mais alta aumenta a estabilidade do oscilador, mas também aumenta o tempo de inicialização. Estes valores são apenas para referência de projeto. Uma vez que cada ressonador possui suas próprias características, o usuário deve consultar o fabricante do ressonador para obter valores apropriados dos componentes externos.

TABELA 14.2: SELEÇÃO DO CAPACITOR PARA OSCILADORES DE CRISTAL

|

Modo |

Freq |

OSC1 (C1) |

OSC2 (C2) |

|

LP |

32 kHz |

15 - 30 pF |

15 - 30 pF |

|

200 kHz |

0 - 15 pF |

0 - 15 pF |

|

XT |

100 kHz |

68 - 150 pF |

150 - 200 pF |

|

2.0 MHz |

15 - 30 pF |

15 - 30 pF |

|

4.0 MHz |

15 - 30 pF |

15 - 30 pF |

|

HS |

8.0 MHz |

15 - 30 pF |

15 - 30 pF |

|

10.0 MHz |

15 - 30 pF |

15 - 30 pF |

|

20.0 MHz |

15 - 30 pF |

15 - 30 pF |

Nota:

Uma capacitância mais alta aumenta a estabilidade do oscilador, mas também aumenta o tempo de inicialização. Estes valores são apenas para referência de projeto. Um resistor em série (RS) pode ser necessário no modo HS, assim como no modo XT, a fim de evitar super-excitação (overdrive) dos cristais especificados para um nível baixo de excitação. Uma vez que cada cristal possui suas próprias características, o usuário deve consultar o fabricante do cristal para obter valores apropriados dos componentes externos.

14.2.3 CIRCUITO DE OSCILADOR EXTERNO A CRISTAL

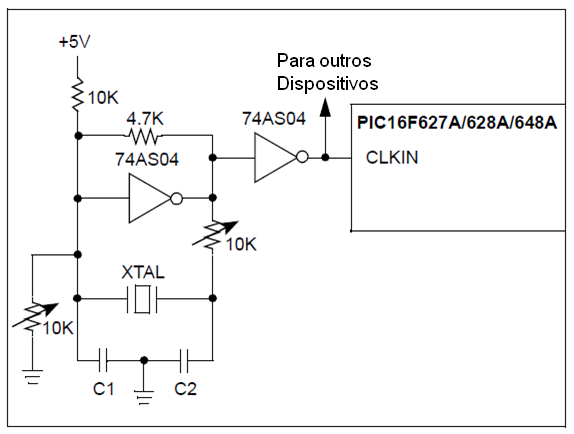

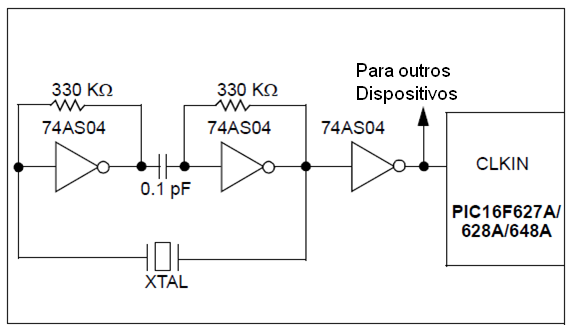

Pode-se utilizar um oscilador monolítico ou pode-se construir um simples circuito de oscilador com portas TTL. Dois tipos de circuito de oscilador a cristal podem ser utilizados; com ressonância em série, ou com ressonância em paralelo.

A Figura 14.2 apresenta a implementação de um circuito de oscilador com ressonância em paralelo. O circuito é projetado para utilizar a frequência fundamental do cristal. O inversor 74AS04 promove a mudança de fase de 180° necessária para um oscilador em paralelo. O resistor de 4,7 kΩ proporciona a realimentação negativa para estabilidade. Os potenciômetros de 10 kΩ ajustam o 74AS04 para a região linear. Este poderia ser utilizado para projetos de osciladores externos.

A Figura 14.3 apresenta um circuito de oscilador com ressonância em série. Este circuito também é projetado para utilizar a frequência fundamental do cristal. O inversor promove uma mudança de fase de 180° em um circuito de oscilador com ressonância em série. Os resistores de 330 kΩ proporcionam a realimentação negativa para ajustar os inversores na região linear.

O oscilador de precisão interno proporciona um clock de sistema com 4MHz fixos (nominal) com VDD = 5V e 25°C. Veja a Seção 17.6 "Especificações e Diagramas de Temporização" para informações sobre a variação de tensão e temperatura.

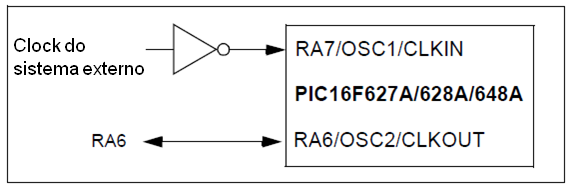

14.2.5 CLOCK EXTERNO DISPONÍVEL

Para aplicações nas quais um clock já está disponível em algum outro local, o usuário pode excitar os microcontroladores PIC16F627A, PIC16F628A e PIC16F648A diretamente, desde que este clock externo atenda os requisitos de temporização de CA/CC listados na Seção 17.6 "Especificações e Diagramas de Temporização". A Figura 14.4 a seguir mostra como um circuito de clock externo deve ser configurado.

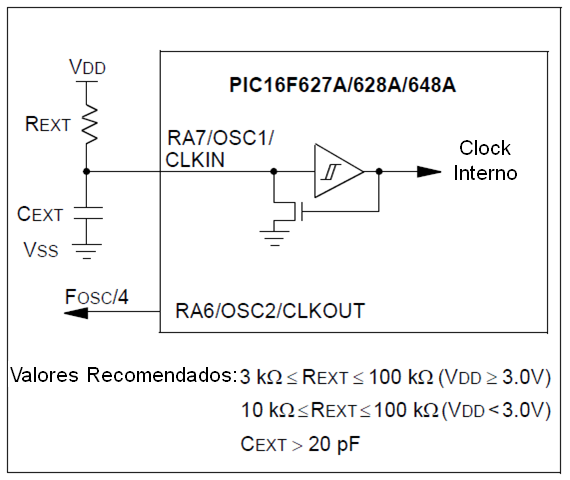

14.2.6 OSCILADOR RC

Para aplicações nas quais uma temporização precisa não é um requisito, a opção do oscilador RC está disponível. A operação e funcionalidade do oscilador RC depende de diversas variáveis. A frequência do oscilador RC é função:

-

da tensão fornecida;

-

dos valores do resistor (REXT) e do capacitor (CEXT);

-

da temperatura de operação.

A frequência do oscilador irá variar de unidade para unidade devido à variação normal de parâmetros do processo. A diferença da capacitância da malha de condutores entre os tipos de encapsulamento também afetará a frequência de oscilação, especialmente para valores baixos de CEXT. O usuário também precisa contabilizar a tolerância dos componentes externos R e C. A Figura 14.5 mostra como a combinação R/C é conectada.

O modo oscilador RC possui duas opções que controlam o pino não-utilizado OSC2. A primeira permite que ele seja utilizado como porta I/O de propósito genérico. A outra configura o pino como saída, fornecendo o sinal FOSC (clock interno dividido por 4) com a finalidade de teste ou de sincronização externa.

14.2.7 CLKOUT

Os microcontroladores PIC16F627A, PIC16F628A e PIC16F648A podem ser configurados para fornecer um sinal de saída de clock através da programação da Palavra de Configuração. A frequência do oscilador dividida por 4 pode ser utilizada para fins de teste ou para sincronizar outra lógica.

14.2.8 CARACTERÍSTICA ESPECIAL: MODOS DE DUPLA VELOCIDADE DO OSCILADOR

Um modo de dupla velocidade do oscilador programável por software é disponibilizado quando os microcontroladores PIC16F627A, PIC16F628A e PIC16F648A são configurados no modo INTOSC do oscilador. Esta característica permite aos usuários selecionar dinamicamente a velocidade do oscilador entre 4 MHz e 48 MHz nominais no modo INTOSC. Aplicações que requerem economia de energia com baixa corrente, mas que não podem tolerar a colocação do dispositivo em Hibernação, podem utilizar este modo.

Existe um delay de tempo associado à transição entre velocidades altas e baixas do oscilador. Este delay da transição de velocidade do oscilador consiste de dois pulsos do clock existente e oito pulsos do clock da nova velocidade. Durante este delay da transição de velocidade do clock, o Clock do Sistema é paralisado, fazendo o processador ficar congelado no tempo. Durante este delay, o contador do programa e o CLKOUT param.

O bit OSCF no registrador PCON é utilizado para controlar o modo de Dupla Velocidade. Veja a Seção 4.2.2.6 "Registrador PCON", Registrador 4.6.

14.3 Reinicialização

Os microcontroladores PIC16F627A, PIC16F628A e PIC16F648A possuem diferentes tipos de reinicialização:

-

Reinicialização de Power-on (POR)

-

Reinicialização MCLR durante a operação normal

-

Reinicialização MCLR durante a Hibernação

-

Reinicialização WDT (operação normal)

-

Reativação WDT (após Hibernação)

-

Reinicialização de Brown-out (BOR)

Alguns registradores não são afetados em nenhuma condição de Reinicialização; o seu status é desconhecido na POR e inalterado em qualquer outra Reinicialização. A maioria dos outros registradores permanece em um "estado de Reinicialização" nas Reinicializações de Power-on, de Brown-out, MCLR, WDT e na Reinicialização MCLR durante a Hibernação. Eles não são afetados por uma reativação WDT, uma vez que esta é vista como uma retomada da operação normal. Os bits TO e PD são ativados ou apagados de forma diferente em diversas situações de Reinicialização, como indicado na Tabela 14.4. Estes bits são utilizados pelo software para determinar a natureza da Reinicialização. Veja a Tabela 14.7 para obter uma descrição completa dos estados de Reinicialização de todos os registradores.

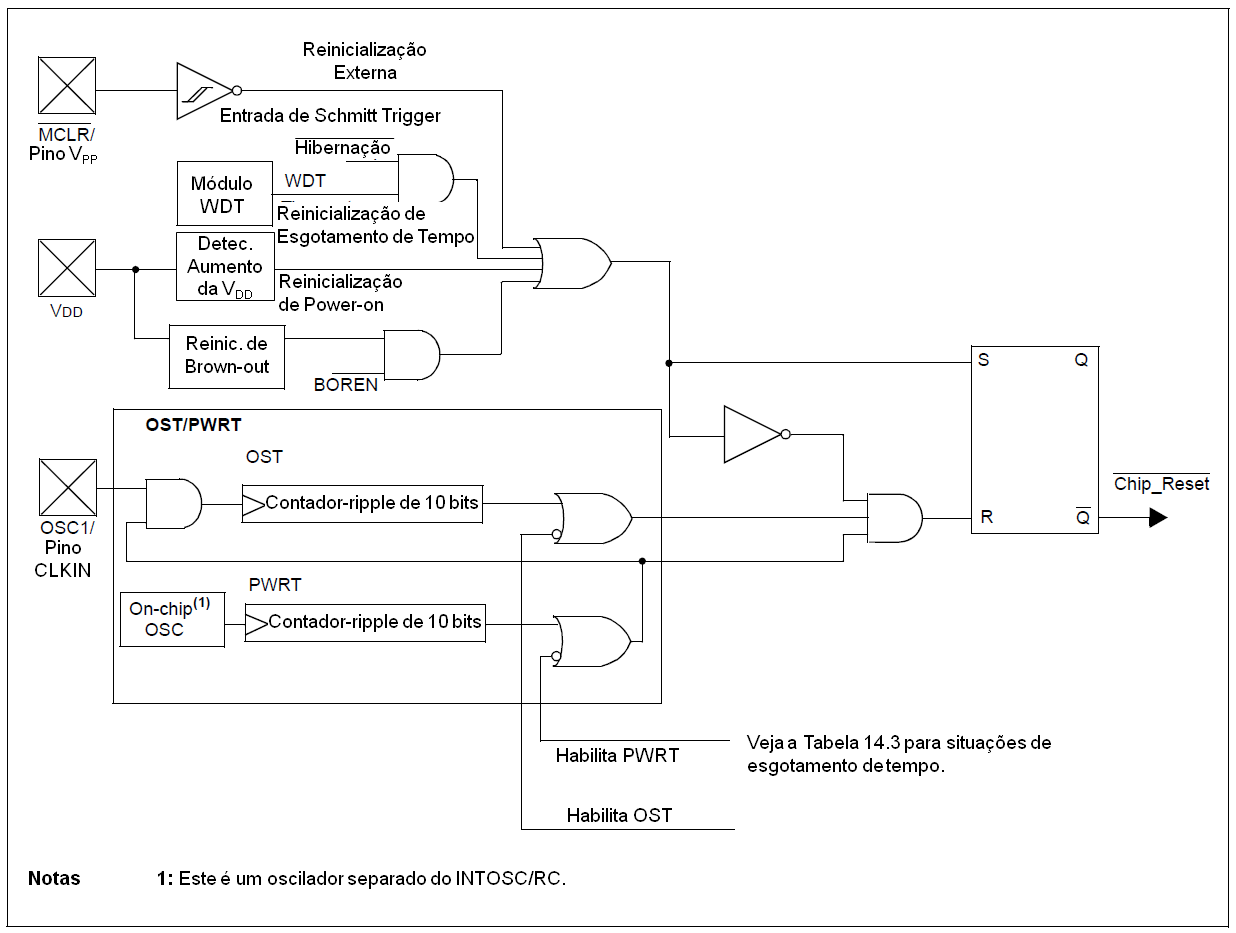

Um diagrama de blocos simplificado do circuito de Reinicialização on-chip é apresentado na Figura 14.6.

O caminho da Reinicialização MCLR possui um filtro de ruído para detectar e ignorar pequenos pulsos. Veja a Tabela 17.7 para a especificação da largura de pulso.

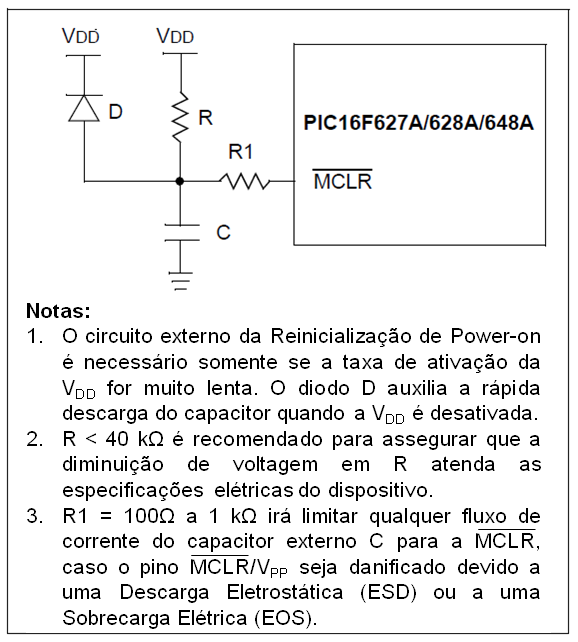

14.4.1 REINICIALIZAÇÃO DE POWER-ON (POR)

A POR on-chip mantém o dispositivo em Reinicialização até que seja detectado um aumento na VDD (na faixa de 1,2 - 1,7 V). É requisitado um tempo máximo para o aumento da VDD. Veja a Seção 17.0 "Especificações Elétricas" para detalhes.

O circuito da POR não produz uma Reinicialização interna quando a VDD diminui.

Quando o dispositivo inicia a operação normal (sai da condição de Reinicialização), os parâmetros de operação do mesmo (tensão, frequência, temperatura, etc.) devem ser atendidos a fim de garantir a operação adequada. Se estas condições não são observadas, o dispositivo deve ser mantido em Reinicialização através da MCLR, BOR ou PWRT até que as condições de operação sejam atingidas.

Para informações adicionais, refira-se à Nota de Aplicação AN607 "Resolução de Problemas de Ativação" (DS00607).

14.4.2 TEMPORIZADOR DE ATIVAÇÃO (PWRT)

O PWRT determina um limite de tempo fixo de 72 ms (nominal) na ativação (POR) ou, caso esteja habilitada, a partir de uma Reinicialização de Brown-out. O PWRT opera em um oscilador RC interno. O chip é mantido em Reinicialização enquanto o PWRT estiver ativo. O delay do PWRT permite que a VDD se eleve até um nível aceitável. Um bit de configuração, PWRTE, pode desabilitar (quando ativado) ou habilitar (quando apagado ou programado) o PWRT. É recomendado que o PWRT seja habilitado quando a Reinicialização de Brown-out estiver habilitada.

O delay no tempo de ativação irá variar de um chip para outro e conforme a VDD, a temperatura e a variação de processo. Consulte os parâmetros de corrente contínua na Tabela 17.7 para detalhes.

14.4.3 TEMPORIZADOR DE INICIALIZAÇÃO DO OSCILADOR (OST)

O OST proporciona um delay de 1024 ciclos do oscilador (a partir da entrada do OSC1), depois de concluído o delay do PWRT. A execução do programa não iniciará até que o limite de tempo do OST esteja esgotado. Isso garante que o oscilador de cristal ou o ressonador tenha iniciado e se estabilizado.

O limite de tempo do OST é utilizado somente para os modos XT, LP e HS, e somente na Reinicialização de Power-on ou na reativação após a Hibernação. Veja a Tabela 17.7.

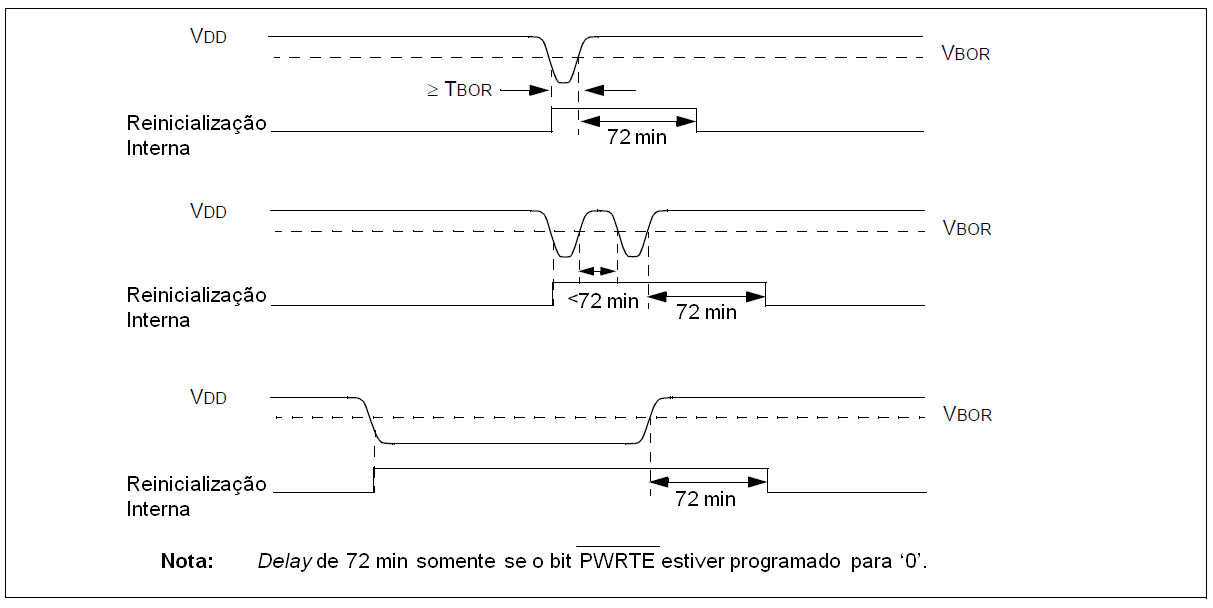

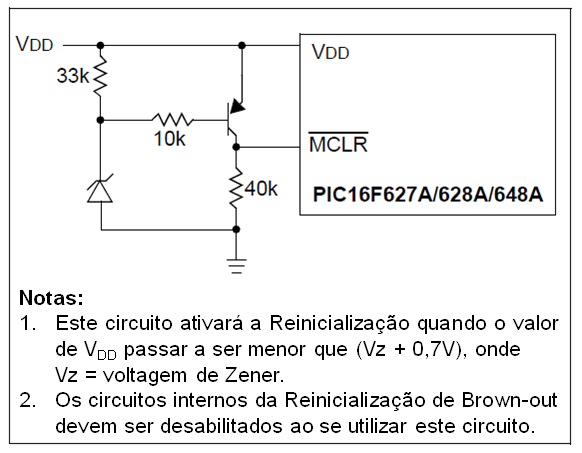

14.4.4 REINICIALIZAÇÃO DE BROWN-OUT (BOR)

Os microcontroladores PIC16F627A, PIC16F628A e PIC16F648A possuem circuitos de BOR on-chip. Um bit de configuração, BOREN, pode desabilitar (quando apagado/ programado) ou habilitar (quando ativado) os circuitos de BOR. Caso o valor da VDD diminua para menos que a VBOR por um tempo maior que TBOR, a situação de brown-out reinicializará o chip. Uma Reinicialização não é garantida caso o valor da VDD diminua para menos que a VBOR por um tempo menor que TBOR. VBOR e TBOR são definidos na Tabela 17.2 e na Tabela 17.7, respectivamente.

Em qualquer Reinicialização (Power-on, Brown-out, Cão-de-Guarda, etc.), o chip permanecerá em Reinicialização até que o valor da VDD aumente para mais que a VBOR (veja a Figura 14.7), O Temporizador de Ativação será agora utilizado, caso esteja habilitado, e manterá o chip em Reinicialização por 72 ms adicionais.

Caso o valor da VDD diminua para menos que a VBOR enquanto o Temporizador de Ativação estiver funcionando, o chip retornará para uma Reinicialização de Brown-out, e o Temporizador de Ativação será reinicializado. Quando o valor da VDD aumentar para mais que a VBOR, o Temporizador de Ativação executará uma Reinicialização de 72 ms. A Figura 14.7 apresenta situações típicas de brown-out.

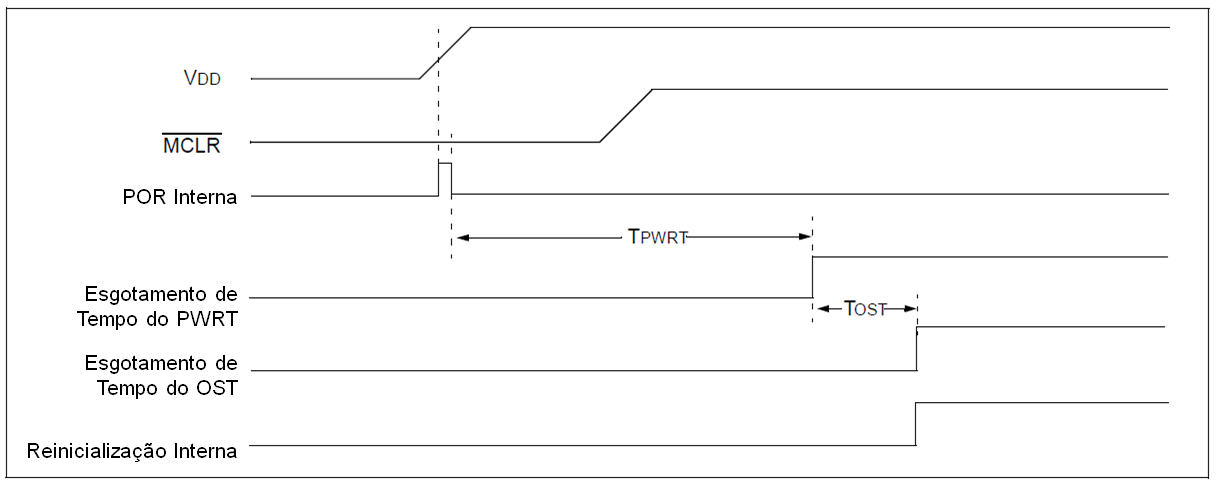

14.4.5 SEQUÊNCIA DO ESGOTAMENTO DE TEMPO

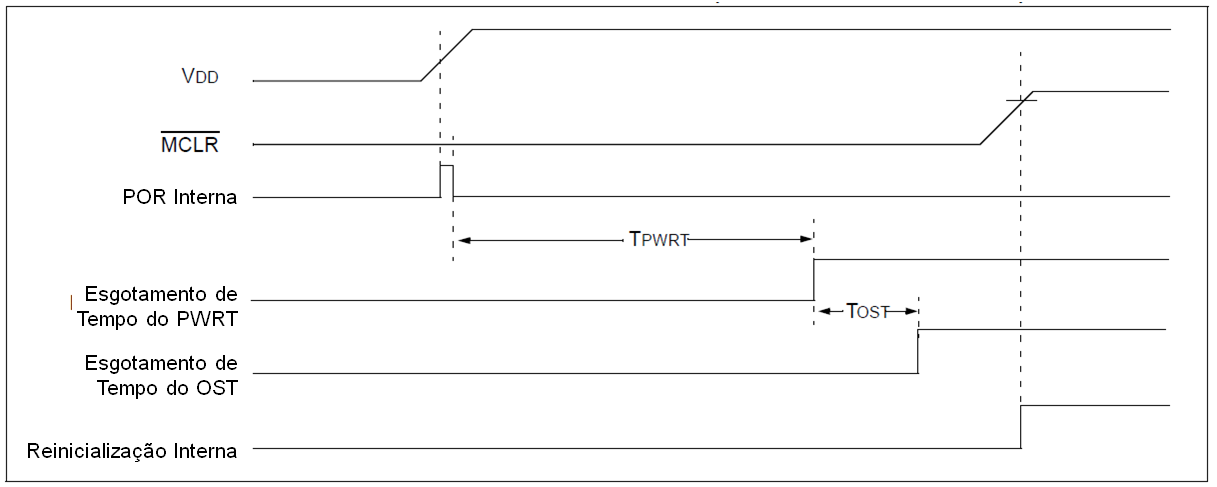

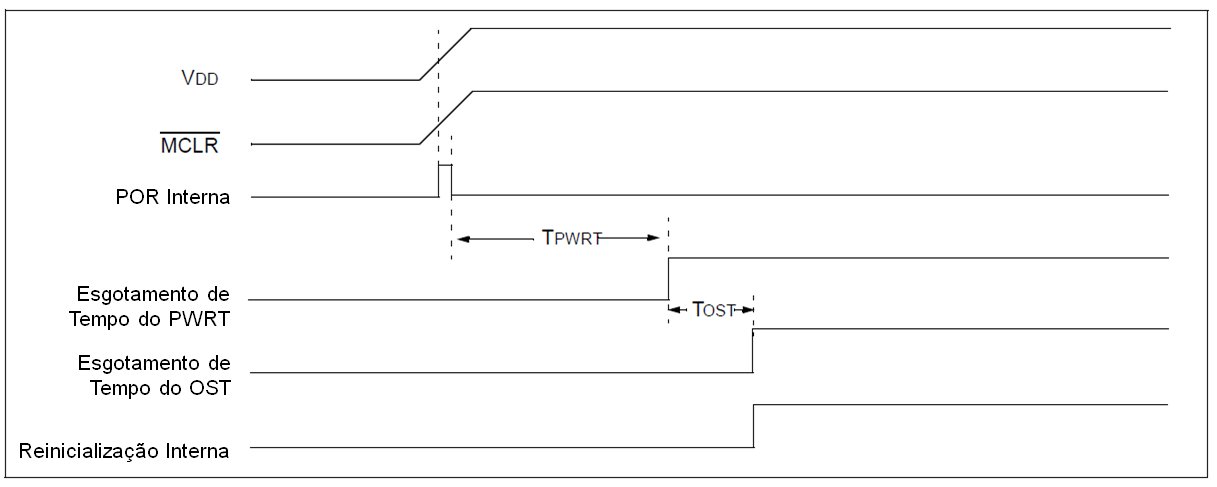

Na ativação, a sequência do esgotamento de tempo é a seguinte: Primeiramente o limite de tempo do PWRT é uilizado, depois de concluida a POR. Depois o OST é ativado. O limite de tempo total irá variar com base na configuração do oscilador e no Status do bit PWRTE. Por exemplo, no modo RC com o bit PWRTE ativado (PWRT desabilitado), não ocorrerá esgotamento de tempo. A Figura 14.8, Figura 14.11 e Figura 14.12 descrevem sequências de esgotamento de tempo.

Uma vez que os esgotamentos de tempo ocorrem a partir do pulso da POR, se a MCLR é mantida suficientemente longa, os esgotamentos de tempo não ocorrerão. Então o aumento da MCLR iniciará a execução imediatamente (veja a Figura 14.11). Isto é útil para a finalidade de testes, ou para sincronizar mais de um dispositivo microcontrolador PIC16F627A, PIC16F628A ou PIC16F648A operando em paralelo.

A Tabela 14.6 apresenta as condições de Reinicialização para alguns registradores especiais, enquanto a Tabela 14.7 apresenta as condições de Reinicialização para todos os registradores.

14.4.6 REGISTRADOR DE STATUS DO CONTROLE DE ENERGIA (PCON)

O registrador PCON/Status, PCON (endereço 8Eh), possui dois bits.

O Bit 0 é BOR (Reinicialização de Brown-out). O BOR é desconhecido na Reinicialização de Power-on. Ele deve ser então ativado pelo usuário e checado em Reinicializações subsequentes, para verificar se BOR=0, indicando que ocorreu um brown-out. O bit de Status BOR é do tipo "indiferente" e não é necessariamente previsível se o circuito de brown-out estiver desabilitado (configurando-se o bit BOREN = 0 na Palavra de Configuração).

O Bit 1 é POR (Reinicialização de Power-on). Ele fica em '0' na Reinicialização de Power-on, e não é afetado em outras situações. O usuário deve escrever um '1' neste bit depois da Reinicialização de Power-on. Em uma Reinicialização subsequente, caso o POR seja '0', ele indicará que uma Reinicialização de Power-on deve haver ocorrido (VDD deve haver diminuido demasiadamente).

TABELA 14.3: ESGOTAMENTO DE TEMPO EM VÁRIAS SITUAÇÕES

|

Configuração do Oscilador |

Temporizador de Ativação |

Reinicialização de Brown-out |

Reativação após Hibernação |

|

PWRTE = 0 |

PWRTE = 1 |

PWRTE = 0 |

PWRTE = 1 |

|

XT, HS, LP |

72 ms + 1024∙TOSC |

1024∙TOSC |

72 ms + 1024∙TOSC |

1024∙TOSC |

1024∙TOSC |

|

RC, EC |

72 ms |

--- |

72 ms |

--- |

--- |

|

INTOSC |

72 ms |

--- |

72 ms |

--- |

6 μs |

|

POR |

BOR |

TO |

PD |

Condição |

|

0 |

X |

1 |

1 |

Reinicialização de Power-on |

|

0 |

X |

0 |

X |

Ilegal, TO é ativado no POR |

|

0 |

X |

X |

0 |

Ilegal, PD é ativado no POR |

|

1 |

0 |

X |

X |

Reinicialização de Brown-out |

|

1 |

1 |

0 |

u |

Reinicialização WDT |

|

1 |

1 |

0 |

0 |

Reativação (após Hibernação) WDT |

|

1 |

1 |

u |

u |

Reinicialização MCLR durante a operação normal |

|

1 |

1 |

1 |

0 |

Reinicialização MCLR durante a Hibernação |

Legenda:

u = inalterado (unchanged)

x = desconhecido

TABELA 14.5: RESUMO DOS REGISTRADORES ASSOCIADOS À REINICIALIZAÇÃO DE BROWN-OUT

|

Endereço |

Nome |

Bit 7 |

Bit 6 |

Bit 5 |

Bit 4 |

Bit 3 |

Bit 2 |

Bit 1 |

Bit 0 |

Valor na Reinicialização POR |

Valor em Todas as Outras Reinicializações(1) |

|

03h, 83h, 103h, 183h |

STATUS |

IRP |

RP1 |

RPO |

TO |

PD |

Z |

DC |

C |

0001 1xxx |

000q quuu |

|

8Eh |

PCON |

--- |

--- |

--- |

--- |

OSCF |

--- |

POR |

BOR |

---- 1-0x |

---- u-uq |

Legenda:

x = desconhecido

u = inalterado (unchanged)

- = não implementado, lido como '0'

q = o valor depende da condição

células sombreadas = não utilizadas pela Reinicialização de Brown-out

Nota 1: Outras Reinicializações (que não a Power-up): MCLR, de Brown-out e de Temporizador Cão-de-Guarda durante a operação normal.

|

Condição |

Contador do Programa |

Registrador Especial |

Registrador PCON |

|

Reinicialização de Power-on |

000h |

0001 1xxx |

---- 1-0x |

|

Reinicialização MCLR durante a operação normal |

000h |

000u uuuu |

---- 1-uu |

|

Reinicialização MCLR durante a Hibernação |

000h |

0001 0uuu |

---- 1-uu |

|

Reinicialização WDT |

000h |

0000 uuuu |

---- 1-uu |

|

Reativação (após Hibernação) WDT |

PC + 1 |

uuu0 0uuu |

---- u-uu |

|

Reinicialização de Brown-out |

000h |

000x xuuu |

---- 1-u0 |

|

Interrupção da Reativação após Hibernação |

PC + 1(1) |

uuu1 0uuu |

---- u-uu |

Legenda:

u = inalterado (unchanged)

x = desconhecido

- = bit não implementado, lido como '0'

Nota 1: Quando a reativação (após a Hibernação) ocorre devido a um bit de interrupção e de habilitação global, o GIE é ativado, o PC é carregado com o vetor de interrupção (0004h) após a execução do PC + 1.

|

Registrador |

Endereço |

Reinicialização de Power-on |

-

Reinicialização MCLR durante a operação normal

-

Reinicialização MCLR durante a Hibernação

-

Reinicialização WDT

-

Reinicialização de Brown-out(1)

|

-

Reativação após Hibernação(7) através de interrupção

-

Reativação após Hibernação(7) através do esgotamento de tempo do WDT

|

|

W |

--- |

xxxx xxxx |

uuuu uuuu |

uuuu uuuu |

|

INDF |

00h, 80h, 100h, 180h |

--- |

--- |

--- |

|

TMR0 |

01h, 101h |

xxxx xxxx |

uuuu uuuu |

uuuu uuuu |

|

PCL |

02h, 82h, 102h, 182h |

0000 0000 |

0000 0000 |

PC + 1(3) |

|

STATUS |

03h, 83h, 103h, 183h |

0001 1xxx |

000q quuu(4) |

uuuq 0uuu(4) |

|

FSR |

04h, 84h, 104h, 184h |

xxxx xxxx |

uuuu uuuu |

uuuu uuuu |

|

PORTA |

05h |

xxxx 0000 |

xxxx 0000 |

uuuu uuuu |

|

PORTB |

06h, 106h |

xxxx xxxx |

uuuu uuuu |

uuuu uuuu |

|

PCLATH |

0Ah, 8Ah, 10Ah, 18Ah |

---0 0000 |

---0 0000 |

---u uuuu |

|

INTCON |

0Bh, 8Bh, 10Bh, 18Bh |

0000 000x |

0000 000u |

uuuu uqqq(2) |

|

PIR1 |

0Ch |

0000 -000 |

0000 -000 |

qqqq -qqq(2) |

|

TMR1L |

0Eh |

xxxx xxxx |

uuuu uuuu |

uuuu uuuu |

|

TMR1H |

0Fh |

xxxx xxxx |

uuuu uuuu |

uuuu uuuu |

|

T1CON |

10h |

--00 0000 |

--uu uuuu(6) |

--uu uuuu |

|

TMR2 |

11h |

0000 0000 |

0000 0000 |

uuuu uuuu |

|

T2CON |

12h |

-000 0000 |

-000 0000 |

-uuu uuuu |

|

CCPR1L |

15h |

xxxx xxxx |

uuuu uuuu |

uuuu uuuu |

|

CCPR1H |

16h |

xxxx xxxx |

uuuu uuuu |

uuuu uuuu |

|

CCP1CON |

17h |

--00 0000 |

--00 0000 |

--uu uuuu |

|

RCSTA |

18h |

0000 000x |

0000 000x |

uuuu uuuu |

|

TXREG |

19h |

0000 0000 |

0000 0000 |

uuuu uuuu |

|

RCREG |

1Ah |

0000 0000 |

0000 0000 |

uuuu uuuu |

|

CMCON |

1Fh |

0000 0000 |

0000 0000 |

uu-- uuuu |

|

OPTION |

81h, 181h |

1111 1111 |

1111 1111 |

uuuu uuuu |

|

TRISA |

85h |

1111 1111 |

1111 1111 |

uuuu uuuu |

|

TRISB |

86h, 186h |

1111 1111 |

1111 1111 |

uuuu uuuu |

|

PIE1 |

8Ch |

0000 -000 |

0000 -000 |

uuuu -uuu |

|

PCON |

8Eh |

---- 1-0x |

---- 1-uq(1, 5) |

---- u-uu |

|

PR2 |

92h |

1111 1111 |

1111 1111 |

uuuu uuuu |

|

TXSTA |

98h |

0000 -010 |

0000 -010 |

uuuu -uuu |

|

SPBRG |

99h |

0000 0000 |

0000 0000 |

uuuu uuuu |

|

EEDATA |

9Ah |

xxxx xxxx |

uuuu uuuu |

uuuu uuuu |

|

EEADR |

9Bh |

xxxx xxxx |

uuuu uuuu |

uuuu uuuu |

|

EECON1 |

9Ch |

---- x000 |

---- q000 |

---- uuuu |

|

EECON2 |

9Dh |

--- |

--- |

--- |

|

VRCON |

9Fh |

000- 0000 |

000- 0000 |

uuu- uuuu |

Legenda:

u = inalterado (unchanged)

x = desconhecido

- = bit não implementado, lido como '0'

q = o valor depende da condição

Notas:

1: Se a VDD diminui muito, a Reinicialização de Power-on será ativada e os registradores serão afetados de forma diferente.

2: Um ou mais bits no INTCON e no PIR1 serão afetados (de forma a causar a reativação).

3: Quando a reativação é causada por uma interrupção e o bit GIE é ativado, o PC é carregado com o vetor de interrupção (0004h).

4: Veja a Tabela 14.6 para o valor da Reinicialização para a condição específica.

5: Caso a Reinicialização tenha ocorrido devido a um brown-out, então o bit 0 = 0. Todas as outras reinicializações causarão bit 0 = u.

6: Reinicialização para '--00 0000' em uma Reinicialização de Brown-out (BOR).

7: Periféricos que geram interrupções para reativação após a Hibernação irão alterar os bits resultantes nos registradores associados.

FIGURA 14.9: SEQUÊNCIA DE ESGOTAMENTO DE TEMPO NO POWER UP (MCLR NÃO RELACIONADA À VDD): CASO 2

FIGURA 14.10: SEQUÊNCIA DE ESGOTAMENTO DE TEMPO NO POWER UP (MCLR RELACIONADA À VDD)

FIGURA 14.13: CIRCUITO 2 EXTERNO DE PROTEÇÃO CONTRA BROWN-OUT

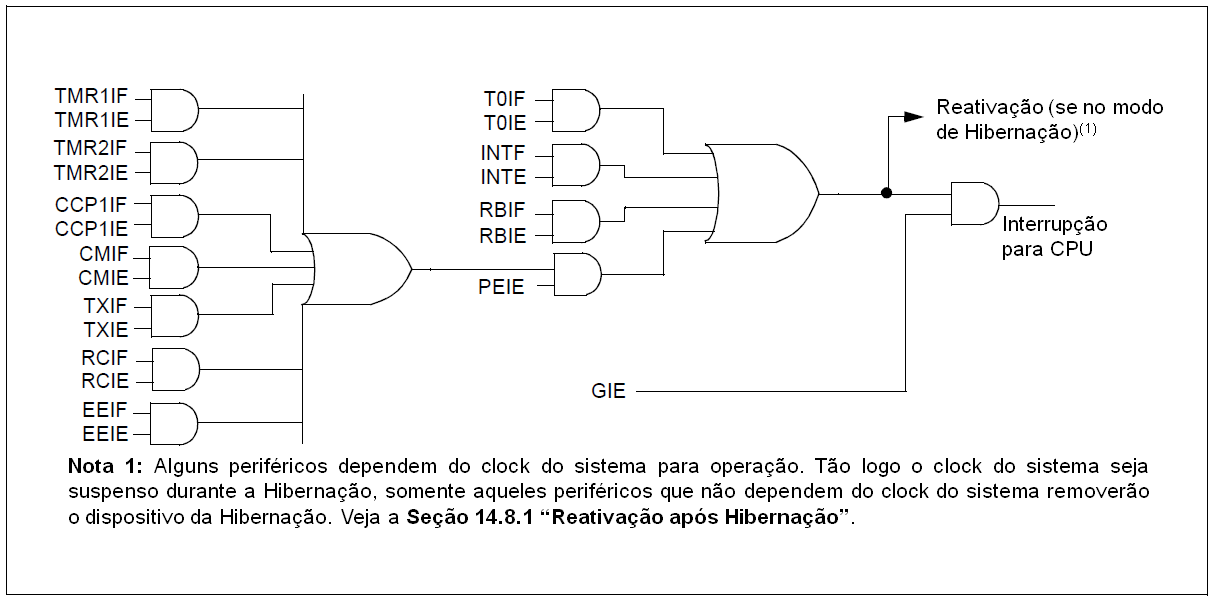

14.5 Interrupções

Os microcontroladores PIC16F627A, PIC16F628A e PIC16F648A possuem 10 fontes de interrupção:

-

Interrupção Externa do RB0/INT

-

Interrupção por Overflow do TMR0

-

Interrupções por Alteração da PORTB (pinos RB<7:4>)

-

Interrupção do Comparador

-

Interrupção TX do USART

-

Interrupção RX do USART

-

Interrupção do CCP

-

Interrupção por Overflow do TMR1

-

Interrupção por Match do TMR2

-

Interrupção da Memória de Dados EEPROM

O registrador de Controle de Interrupção (INTCON) grava as solicitações de interrupção individuais em bits sinalizadores. Ele também possui bits de habilitação de interrupção individual e global.

Um bit de Habilitação de Interrupção Global, GIE (INTCON<7>), habilita (se ativado) todas as interrupções não-mascaradas, ou desabilita (se apagado) todas as interrupções. Interrupções individuais podem ser desabilitadas através dos seus respectivos bits de habilitação no registrador INTCON. O GIE é apagado na Reinicialização.

A instrução "retornar-da-interrupção", RETFIE, encerra a rotina de interrupção, e também ativa o bit GIE, o que reabilita as interrupções do RB0/INT.

Os sinalizadores da interrupção do pino INT, da interrupção por alteração da porta RB e da interrupção por overflow do TMR0 estão localizados no registrador INTCON.

O sinalizador de interrupção periférica está localizado no registrador especial PIR1. O bit de habilitação de interrupção correspondente está localizado nos registradores especiais PIE1.

Quando uma interrupção recebe uma resposta, o GIE é apagado para desabilitar qualquer outra interrupção, o endereço de retorno é colocado na pilha e o PC é carregado com 0004h. Uma vez na rotina de serviço da interrupção, a(s) fonte(s) da interrupção podem ser determinadas pesquisando-se os bits sinalizadores (flags) de interrupção. O(s) bit(s) sinalizadores de interrupção devem ser apagados pelo software antes da reabilitação das interrupções, para evitar interrupções recursivas do pino RB0/INT.

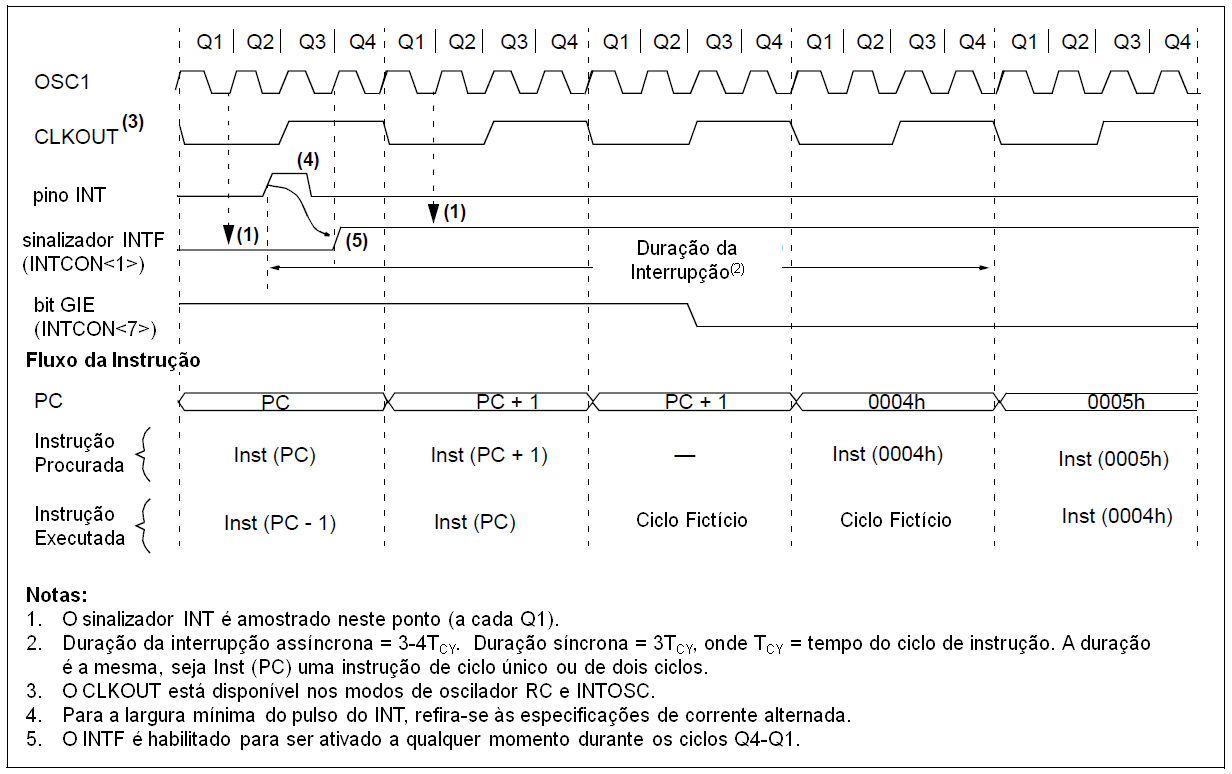

Para eventos de interrupção externa, tais como a interrupção por alteração do pino INT ou da PORTB, a latência da interrupção será de três ou quatro ciclos de instrução. A duração exata depende de quando ocorre o evento de interrupção (Figura 14.15). A duração é a mesma para instruções de um ou dois ciclos. Uma vez na rotina de serviço da interrupção, a(s) fonte(s) da interrupção podem ser determinadas pesquisando-se os bits sinalizadores de interrupção. O(s) bit(s) sinalizadores de interrupção devem ser apagados pelo software antes da reabilitação das interrupções, para evitar múltiplas solicitações de interrupção.

Nota 1: Os bits sinalizadores de interrupção individuais são ativados sem considerar o status do seu bit de máscara correspondente ou do bit GIE.

Nota 2: Quando uma instrução que apaga o bit GIE é executada, quaisquer interrupções que estavam pendentes para execução no próximo ciclo são ignoradas. A CPU executará um NOP no ciclo imediatamente seguinte à instrução que apaga o bit GIE. As interrupções que foram ignoradas ainda estarão pendentes para serem executadas quando o bit GIE for novamente ativado.

FIGURA 14.14: LÓGICA DE INTERRUPÇÃO

14.5.1 INTERRUPÇÃO DO RB0/INT

A interrupção externa no pino RB0/INT é disparada na borda do sinal aplicado; tanto na borda de subida, caso o bit INTEDG (OPTION<6>) for ativado, quanto na borda de descida, se o bit INTEDG for apagado. Quando uma borda válida aparece no pino RB0/INT, o bit INTF (INTCON<1>) é ativado. Esta interrupção pode ser desabilitada apagando-se o bit de controle INTE (INTCON<4>).O bit INTF deve ser apagado pelo software na rotina de serviço de interrupção, antes da reabilitação desta interrupção. A interrupção do RB0/INT pode remover o processador da Hibernação, se o bit INTE tiver sido ativado antes do início da Hibernação. O status do bit GIE determina se o processador deriva ou não para o vetor de interrupção após sair da Hibernação. Veja a Seção 14.8 "Modo de Desativação (Hibernação)" para detalhes sobre Hibernação, e a Figura 14.7 para a temporização da reativação após a Hibernação através da interrupção do RB0/INT.

14.5.2 INTERRUPÇÃO DO TMR0

Um overflow (FFh→00h) no registrador TMR0 ativará o bit T0IF (INTCON<2>). A interrupção pode ser habilitada/desabilitada ativando-se/apagando-se o bit T0IE (INTCON<5>). Para a operação do módulo Timer0, veja a Seção 6.0 "Módulo Timer0".

14.5.3 INTERRUPÇÃO DA PORTB

Uma alteração de entrada na PORTB <7:4> ativa o bit RBIF (INTCON<0>). A interrupção pode ser habilidata/desabilitada ativando-se/apagando-se o bit RBIE (INTCON<3>). Para a operação da PORTB, veja a Seção 5.2 "Registradores PORTB e TRISB".

Nota:

Caso ocorra uma alteração no pino I/O quando a operação de leitura estiver sendo executada (inicia durante o ciclo Q2 e se encerra antes do início do ciclo Q3), então o sinalizador de interrupção RBIF pode não ser ativado.

14.5.4 INTERRUPÇÃO DO COMPARADOR

Veja a Seção 10.6 "Interrupções do Comparador" para a descrição completa das interrupções do comparador.

TABELA 14.8: RESUMO DOS REGISTRADORES DE INTERRUPÇÃO

|

Endereço |

Nome |

Bit 7 |

Bit 6 |

Bit 5 |

Bit 4 |

Bit 3 |

Bit 2 |

Bit 1 |

Bit 0 |

Valor na Reinicialização POR |

Valor em Todas as Outras Reinicializações(1) |

|

0Bh, 8Bh, 10Bh, 18Bh |

INTCON |

GIE |

PEIE |

T0IE |

INTE |

RBIE |

T0IF |

INTF |

RBIF |

0000 000x |

0000 000u |

|

0Ch |

PIR1 |

EEIF |

CMIF |

RCIF |

TXIF |

--- |

CCP1IF |

TMR2IF |

TMR1IF |

0000 -000 |

0000 -000 |

|

8Ch |

PIE1 |

EEIE |

CMIE |

RCIE |

TXIE |

--- |

CCP1IE |

TMR2IE |

TMR1IE |

0000 -000 |

0000 -000 |

Legenda:

x = desconhecido

u = inalterado (unchanged)

- = não implementado, lido como '0'

células sombreadas = não utilizadas

Nota 1: Outras Reinicializações (que não a Power-up): MCLR, de Brown-out e de Temporizador Cão-de-Guarda durante a operação normal.

14.6 Gravação do Contexto durante Interrupções

Durante uma interrupção, somente o valor de retorno do PC é gravado na pilha. Tipicamente, os usuários podem desejar gravar registradores-chave durante uma interrupção (p. ex., o registrador W e o registrador de Status). Isto pode ser implementado pelo software.

O Exemplo 14.1 armazena e restaura os registradores de Status e W. O registrador do usuário, W_TEMP, deve ser definido em uma posição da memória comum (i. e., o W_TEMP é definido em 0x70h do Banco 0, e portanto é acessível em 0xF0, 0x170 e 0x1F0 (ver 4.2 Organização da Memória de Dados)). O Exemplo 14.1:

-

Armazena o registrador W

-

Armazena o registrador de Status

-

Executa o código ISR

-

Restaura o Status (e o registrador do bit de seleção do banco)

-

Restaura o registrador W

MOVWF W_TEMP ;copiar W para o registrador TEMP,

;pode ser em qualquer banco

SWAPF STATUS,W ;trocar o status a ser

;salvo por W

BCF STATUS,RP0 ;alterar para o banco 0

;independentemente do banco atual

MOVWF STATUS_TEMP ;salvar o status para o

;registrador do banco 0

:

:(ISR)

:

SWAPF STATUS_TEMP,W ;trocar o registrados

;por W, configura o banco para

;o status original

MOVWF STATUS ;move W para o registrador STATUS

SWAPF W_TEMP,F ;troca W_TEMP

SWAPF W_TEMP,W ;troca W_TEMP por W

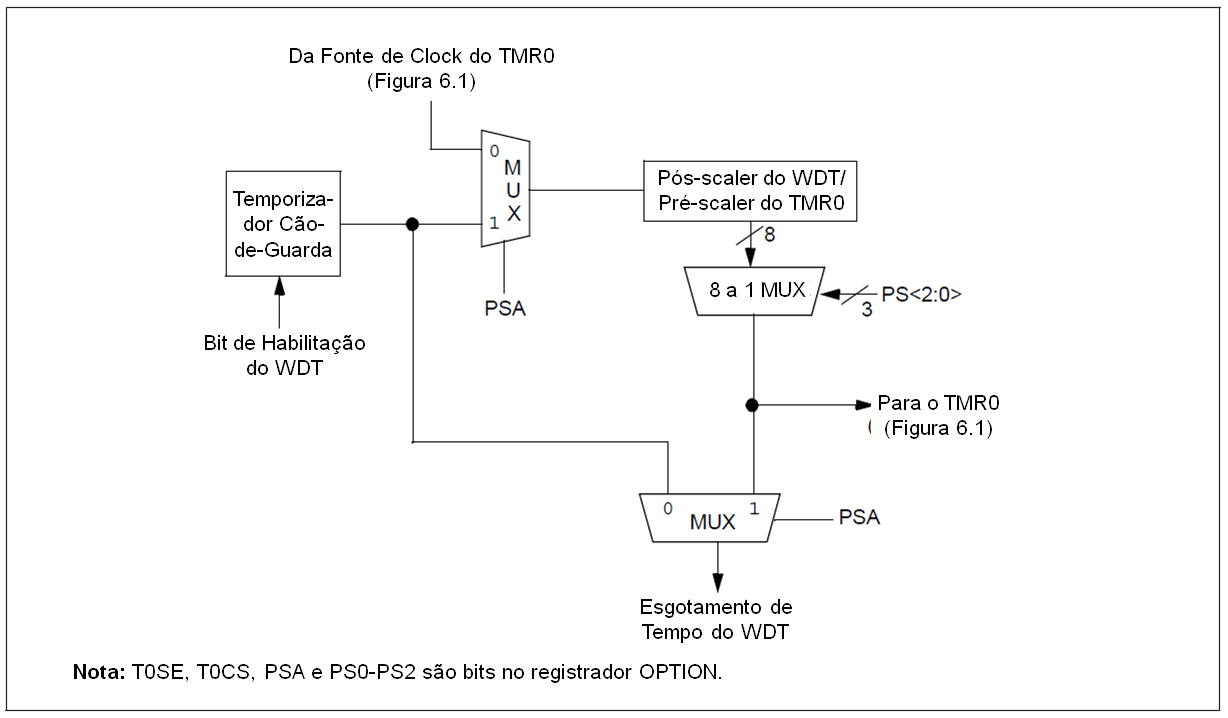

14.7 Temporizador Cão-de-Guarda (WDT)

O Temporizador Cão-de-Guarda é um oscilador RC de funcionamento livre on-chip que não necessita de componentes externos. Este oscilador RC é separado do oscilador RC do pino CLKIN. Isto significa que o WDT funcionará, mesmo que o clock nos pinos OSC1 e OSC2 do dispositivo tenham sido paralisados, por exemplo, pela execução de uma instrução SLEEP. Durante a operação normal, um esgotamento de tempo do WDT gera uma Reinicialização do dispositivo. Se o dispositivo estiver no modo de Hibernação, um esgotamento de tempo do WDT faz o dispositivo ser reativado e continuar com a operação normal. O WDT pode ser permanentemente desabilitado programando-se o bit de configuração WDTE como apagado. (Seção 14.1 "Bits de Configuração").

14.7.1 PERÍODO DO WDT

O WDT possui um período-limite de tempo nominal de 18 ms (sem pré-scaler). Os períodos-limite de tempo variam com a temperatura, com a VDD e com variações do processo de um dispositivo para outro (veja as Especificações de Corrente Contínua, Tabela 17.7). Se períodos-limite de tempo mais longos são desejados, um pós-scaler com uma razão de divisão de até 1:128 pode ser atribuído ao WDT sob controle do software, escrevendo-se no registrador OPTION. Portanto, períodos-limite de tempo de até 2,3 segundos podem ser obtidos.

As instruções CLRWDT e SLEEP apagam o WDT e o pós-scaler, caso atribuídas ao WDT, e o previnem de esgotar o tempo, gerando uma Reinicialização do dispositivo.

O bit TO no registrador de Status será apagado em um esgotamento de tempo do Temporizador Cão-de-Guarda.

14.7.2 CONSIDERAÇÕES SOBRE A PROGRAMAÇÃO DO WDT

Deve-se levar em conta que, sob condições de pior caso (VDD = Min., Temperatura = Max., máx. pré-scaler do WDT), pode-se levar vários segundos antes que ocorra um esgotamento de tempo do WDT.

FIGURA 14.16: DIAGRAMA DE BLOCOS DO TEMPORIZADOR CÃO-DE-GUARDA

TABELA 14.9: RESUMO DOS REGISTRADORES DO TEMPORIZADOR CÃO-DE-GUARDA

|

Endereço |

Nome |

Bit 7 |

Bit 6 |

Bit 5 |

Bit 4 |

Bit 3 |

Bit 2 |

Bit 1 |

Bit 0 |

Valor na Reinicialização POR |

Valor em Todas as Outras Reinicializações |

|

2007h |

CONFIG |

LVP |

BOREN |

MCLRE |

FOSC2 |

PWRTE |

WDTE |

FOSC1 |

FOSC0 |

uuuu uuuu |

uuuu uuuu |

|

81h, 181h |

OPTION |

RBPU |

INTEDG |

T0CS |

T0SE |

PSA |

PS2 |

PS1 |

PS0 |

1111 1111 |

1111 1111 |

Legenda:

x = desconhecido

u = inalterado (unchanged)

- = não implementado, lido como '0'

células sombreadas = não utilizadas

O modo de Desativação é acionado pela execução de uma instrução SLEEP.

Quando habilitado, o Temporizador Cão-de-Guarda será apagado, porém continua funcionando, o bit PD no registrador de Status é apagado, o bit TO é ativado, e o driver do oscilador é desligado. As portas I/O permanecem no status em que estavam antes da instrução SLEEP ter sido executada (conduzindo em nível alto ou baixo, ou em alta impedância).

Para um menor consumo de energia neste modo, todos os pinos I/O devem estar em VDD ou em VSS, sem nenhum circuito externo drenando corrente do pino I/O e dos comparadores, e a VREF deve ser desabilitada. Os pinos I/O que forem entradas de alta impedância devem ser mantidos altos ou baixos externamente, a fim de evitar inversões de corrente causadas por entradas flutuantes. A entrada do T0CKI deve também estar em VDD ou VSS, para um menor consumo de energia. A contribuição dos pull-ups on-chip na PORTB deve ser levada em conta.

O pino MCLR deve estar em um nível lógico alto (VIHMC).

Nota:

Deve-se notar que uma Reinicialização gerada por um esgotamento de tempo do WDT não conduz o pino MCLR para baixo.

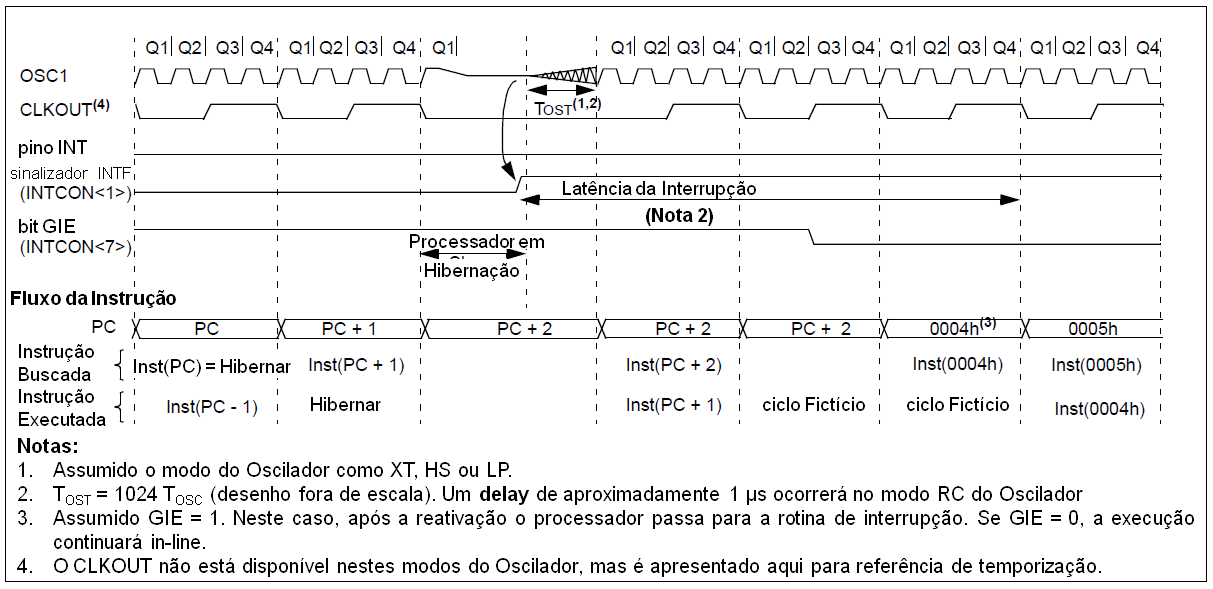

14.8.1 REATIVAÇÃO APÓS A HIBERNAÇÃO

O dispositivo pode sair da Hibernação através de um dos seguintes eventos:

-

Entrada de Reinicialização externa no pino MCLR

-

Reativação do Temporizador Cão-de-Guarda (caso o WDT tiver sido habilitado)

-

Interrupção a partir do pino RB0/INT, alteração da porta RB, ou qualquer interrupção periférica que esteja ativa na Hibernação.

O primeiro evento causará uma Reinicialização do dispositivo. Os dois eventos seguintes são considerados uma continuação da execução do programa. Os bits TO e PD no registrador de Status podem ser utilizados para determinar a causa da Reinicialização do dispositivo. O bit PD, que é ativado quando o dispositivo é ligado, é apagado quando a Hibernação é solicitada. O bit TO é apagado caso tenha ocorrido uma reativação do WDT.

Quando a instrução SLEEP estiver sendo executada, a próxima instrução (PC + 1) é previamente buscada. Para a reativação do dispositivo através de um evento de interrupção, o bit de habilitação da interrupção correspondente deve ser ativado (habilitado). A reativação é independente do estado do bit GIE. Se o bit GIE estiver apagado (desabilitado), o dispositivo continua a execução na instrução seguinte à SLEEP. Se o bit GIE estiver ativado (habilitado), o dispositivo executa a instrução depois da SLEEP e então desvia para o endereço de interrupção (0004h). Nos casos em que a execução da instrução seguinte à SLEEP não for desejada, o usuário deve ter uma instrução NOP depois da instrução SLEEP.

Nota:

Caso as interrupções globais estejam desabilitadas (o GIE esteja apagado), mas qualquer fonte de interrupção tenha o seu bit de habilitação de interrupção e também o seu bit de sinalização de interrupção ativos, o dispositivo não entrará em Hibernação. A instrução SLEEP será executada como uma instrução NOP.

O WDT é apagado quando o dispositivo sai da Hibernação, independentemente da fonte da reativação.

FIGURA 14.17: SAÍDA DA HIBERNAÇÃO ATRAVÉS DE INTERRUPÇÃO

14.9 Proteção de Código

Quando o bit de proteção de código é apagado (Proteção de Código habilitada), o conteúdo das posições de memória do programa é lido como '0'. Veja a "Especificação de Programação da Memória EEPROM dos PIC16F627A/628A/648A" (DS41196) para detalhes.

Nota:

Somente uma função Apagar a Memória Temporária pode ativar os bits CP e CPD através da desativação da proteção de código. Todos os dados das memórias EEPROM e Flash do programa serão apagados para desativar a proteção de código.

14.10 Posições de ID do Usuário

Quatro posições da memória (2000h-2003h) são designadas como endereços de ID do usuário, nos quais ele pode armazenar somas de verificação ou outros números de identificação de código. Estas posições não são acessíveis durante a execução normal, mas podem ser lidas e escritas no modo Programar/Verificar. Somente os 4 bits Menos Significativos das posições de ID do usuário são utilizados para somas de verificação, embora cada posição tenha 14 bits.

14.11 Programação Serial In-CircuitTM (ICSPTM)

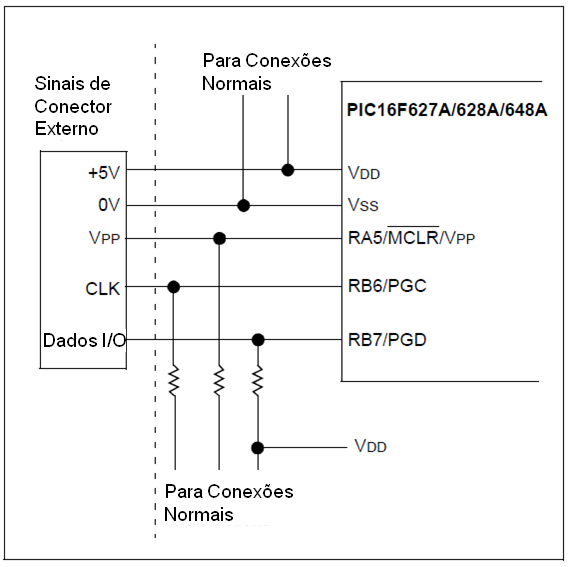

Os microcontroladores PIC16F627A, PIC16F628A e PIC16F648A podem ser programados por programação serial quando estiverem no circuito da aplicação final. Isto é feito de forma simples com duas linhas para clock e dados, e três outras linhas para energia, tensão de terra e tensão de programação. Isso permite aos clientes fabricar placas com dispositivos não-programados e posteriormente programar o microcontrolador imediatamente antes de enviar o produto. Isso também também possibilita que o firmware mais recente ou um firmware customizado seja programado.

O dispositivo é colocado no modo Programar/Verificar mantendo-se os pinos RB6 e RB7 baixos e subindo-se o pino MCLR (VPP) de VIL para VIHH. Veja a "Especificação de Programação da Memória EEPROM dos PIC16F627A/628A/648A" (DS41196) para detalhes. RB6 se torna o clock de programação e o RB7 se torna a entrada dos dados de programação. Tanto o RB6 como o RB7 consistem em entradas do tipo Schmitt Trigger neste modo.

Após a Reinicialização, para colocar o dispositivo no modo Programar/Verificar, o Contador do Programa (PC) está na posição 00h. Um comando de 6 bits é então provido ao dispositivo. Dependendo do comando, 14 bits de dados de programação são então providos para ou do dispositivo, dependendo se o comando foi para gravação ou leitura. Para detalhes completos da programação serial, por favor refira-se à "Especificação de Programação da Memória EEPROM dos PIC16F627A/628A/648A" (DS41196).

Uma típica conexão de Programação Serial In-Circuit é apresentada na Figura 14.18.

14.12 Programação em Baixa Tensão

O bit LVP da Palavra de Configuração habilita a programação em baixa tensão. Este modo permite que o microcontrolador seja programado através da ICSP utilizando-se somente uma fonte de 5V. Este modo elimina a necessidade da tensão VIHH ser colocada no pino MCLR. O bit LVP é normalmente apagado para '1', o que habilita a programação em baixa tensão. Neste modo, o pino RB4/PGM é dedicado à função de programação e deixa de ser um pino I/O de propósito genérico. O dispositivo entrará no modo de Programação quando um '1' for colocado no pino RB4/PGM. O modo de Programação em Alta Tensão ainda está disponível colocando-se a VIHH no pino MCLR.

Nota 1: Enquanto neste modo, o pino RB4 não pode mais ser utilizado como um pino I/O de propósito genérico.

Nota 2: A VDD deve ser 5,0V ∓10% durante operações de apagamento.

Caso o modo de Programação em Baixa Tensão não for utilizado, o bit LVP deve ser programado para '0' de forma que o RB4/PGM se torne um pino digital I/O. Para programar o dispositivo, a tensão VIHH deve ser colocada no MCLR durante a programação. O bit LVP deve ser programado somente quando é dada a entrada na programação com a VIHH no MCLR. O bit LVP não pode ser programado quando é dada a entrada na programação com o RB4/PGM.

Deve-se notar que, uma vez que o bit LVP é programado para '0', somente o modo de Programação em Alta Tensão pode ser utilizado para programar o dispositivo.

14.13 Depurador In-Circuit

Tendo em vista que a depuração (debugging) in-circuit requer a perda do clock, dos pinos de dados e MCLR, o desenvolvimento do ICD 2 da MPLAB® com um dispositivo de 18 pinos não é prático. Um dispositivo especial de 28 pinos PIC16F648A-ICD é utilizado com o ICD2 da MPLAB para prover o clock, os pinos de dados e MCLR em separado, e liberar todos os pinos normalmente disponíveis para o usuário. A depuração de todas as três versões dos microcontroladores PIC16F627A, PIC16F628A e PIC16F648A é suportada pelo PIC16F648A-ICD.

Este dispositivo especial ICD é montado na parte superior de um conector header, e seus sinais são roteados para o conector do ICD 2 da MPLAB. Na parte inferior do header está um soquete de 18 pinos que é plugado no equipamento-alvo do usuário através de um conector de 18 pinos do tipo stand-off.

Quando o pino ICD no dispositivo PIC16F648A-ICD é mantido baixo, a funcionalidade de Depurador In-Circuit é habilitada. Esta função permite a depuração simples quando utilizada com o ICD 2 da MPLAB. Quando o microcontrolador tem esta propriedade habilitada, alguns dos recursos não estão disponíveis para uso genérico. a Tabela 14.10 mostra quais propriedades são consumidas pelo depurador de fundo.

|

pinos I/O |

ICDCLK, ICDDATA |

|

Pilha |

1 nível |

|

Memória do Programa |

Endereço 0h, deve ser NOP

300h-3FEh |

O dispositivo PIC16F648A-ICD com header é fornecido como uma montagem. Veja o Código da Peça Microchip AC 162053.