Tradução: Maria Elisa - Assessoria em Inglês e Alemão

Revisão: Renato Kodaira

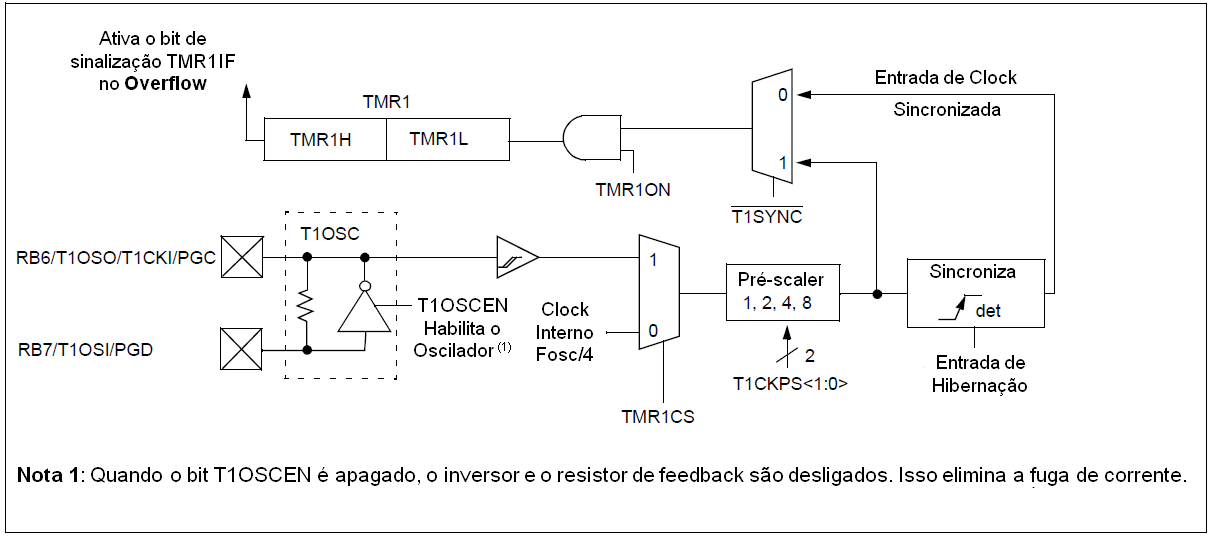

O módulo Timer1 dos microcontroladores PIC16F627A, PIC16F628A e PIC16F648A é um temporizador/contador de 16 bits que consiste em dois registradores de 8 bits (TMR1H e TMR1L) que são acessiveis para leitura e escrita. O par de registradores TMR1 (TMR1H:TMR1L) incrementa de 0000h até FFFFh e volta a 0000h. A interrupção do Timer1, se habilitada, é gerada pelo overflow do par de registradores TMR1, o qual armazena o bit de sinalização de interrupção TMR1IF (PRR<0>).Esta interrupção pode ser habilitada/desabilitada ativando-se/apagando-se o bit de habilitação de interrupção do Timer1 TMR1IE (IPIE<1>).

O Timer1 pode operar de duas formas:

-

Como um temporizador

-

Como um contador

O modo de Operação é determinado pelo bit de seleção de clock, TMR1CS (T1CON<i>).

No modo temporizador, o valor do par de registradores TMR1 incrementa a cada ciclo de instrução. No modo contador, ele incrementa a cada borda de subida da entrada do clock externo.

O Timer1 pode ser habilitado/ desabilitado ativando-se/ apagando-se o bit de controle TMR1ON (T1CON<0>).

O Timer1 também possui uma "entrada de Reinicialização" interna. Esta Reinicialização pode ser gerada pelo módulo CCP (Seção 9.0 "Módulo de Captura/ Comparação/ PWM (CCP)"). O Registrador 7.1 apresenta o registrador de controle do Timer1.

Para os PIC16F627A/628A/648A, quando o oscilador do Timer1 é habilitado (o T1OSCEN é ativado), os pinos RB7/T1OSI/PGD e RB6/T1OSO/T1CKI/PGC se tornam entradas. Isto é, o valor dos TRISB<7:6> é ignorado.

|

|

|

U-0 |

U-0 |

R/W-0 |

R/W-0 |

R/W-0 |

R/W-0 |

R/W-0 |

R/W-0 |

|

--- |

--- |

T1CKPS1 |

T1CKPS0 |

T1OSCEN |

T1SYNC |

TMR1CS |

TMR1ON |

|

bit 7 |

|

|

|

|

|

|

bit 0 |

|

bit 7-6

|

Não Implementados: Lidos como '0'

|

|

bit 5-4 |

T1CKPS<1:0>: Bits de Seleção da Pré-escala do Clock de Entrada do Timer1 |

|

|

11 = valor da pré-escala 1:8 |

|

|

10 = valor da pré-escala 1:4 |

|

|

01 = valor da pré-escala 1:2 |

|

|

00 = valor da pré-escala 1:1

|

|

bit 3 |

T1OSCEN: Bit de Controle de Habilitação do Oscilador do Timer1 |

|

|

1 = oscilador é habilitado |

|

|

0 = oscilador é desligado(1)

|

|

bit 2 |

T1SYNC: Bit de Controle de Sincronização da Entrada do Clock Externo do Timer1 |

|

|

TMR1CS = 1 |

|

|

1 = não sincroniza a entrada do clock externo |

|

|

0 = sincroniza a entrada do clock externo |

|

|

TMR1CS = 0 |

|

|

Este bit é ignorado. O Timer1 utiliza o clock interno quando TMR1CS = 0.

|

|

bit 1 |

TMR1CS: Bit de Seleção da Fonte de Clock do Timer1 |

|

|

1 = clock externo do pino RB6/T1OSO/T1CKI/PGC (na borda de subida) |

|

|

0 = clock interno (Fosc/4)

|

|

bit 0 |

TMR1ON: Bit de Acionamento do Timer1 |

|

|

1 = habilita o Timer1 |

|

|

0 = pára o Timer1

|

|

|

Nota 1: O inversor e o resistor de feedback do oscilador são desligados para eliminar a fuga de corrente.

|

|

|

Legenda:

R = bit de leitura

W = bit de escrita

U = bit não implementado (unimplemented), lido como '0'

-n = valor na POR

'1' = bit está ativado

'0' = bit está apagado

x = bit é desconhecido |

7.1 Operação do Timer1 no Modo Temporizador

O modo temporizador é selecionado apagando-se o bit TMR1CS (T1CON<1>). Neste modo, o clock de entrada para o temporizador é Fosc/4. O bit de controle de sincronização T1SYNC (T1CON<2>) não tem efeito, já que o clock interno está sempre em sincronia.

7.2 Operação do Timer1 no Modo Contador Sincronizado

O modo contador é selecionado ativando-se o bit TMR1CS. Neste modo, o valor do par de registradores TMR1 incrementa em cada borda de subida da entrada do clock no pino RB7/T1OSI/PGD quando o bit T1OSCEN estiver ativado, ou no pino RB6/T1OSO/T1CKI/PGC, quando o bit T1OSCEN estiver apagado.

Se o T1SYNC estiver apagado, então a entrada do clock externo está sincronizada com os clocks de fase internos. A sincronização é realizada depois do estágio do pré-scaler. O estágio do pré-scaler consiste em um contador-ripple (contador por pulsação) assíncrono.

Nesta configuração, durante o modo de Hibernação, o valor do par de registradores TMR1 não incrementará, mesmo que o clock externo esteja presente, pois o circuito de sincronização é desligado. Entretanto, o pré-scaler continuará a incrementar.

7.2.1 TEMPORIZAÇÃO DA ENTRADA DO CLOCK EXTERNO PARA O MODO CONTADOR SINCRONIZADO

Quanto um clock externo é utilizado para o Timer1 no modo Contador Sincronizado, ele deve atender a certos requisitos. O requisito do clock externo se deve à sincronização do clock de fase interno (Tosc). Além disso, existe um delay na incrementação atual no valor do par de registradores TMR1, depois da sincronização.

Quando o pré-scaler está em 1:1, a entrada do clock externo é a mesma que a saída do pré-scaler. A sincronização do T1CKI com os clocks de fase internos é realizada amostrando-se a saída do pré-scaler nos ciclos Q2 e Q4 dos clocks de fase internos. Portanto, é necessário que o T1CKI esteja alto por pelo menos 2 Tosc (e um pequeno delay de 20ns do RC) e baixo por pelo menos 2 Tosc (e um pequeno delay de 20ns do RC). Consulte a Tabela 17.8 na Seção de Especificações Elétricas, parâmetros de temporização 45, 46 e 47.

Quando um pré-scaler é utilizado com uma proporção diferente de 1:1, a entrada do clock externo é dividida pelo pré-scaler do tipo contador-ripple assíncrono, de forma que a saída do pré-scaler seja simétrica. Para que o clock externo atenda ao requisito de amostragem, o contador-ripple deve ser levado em conta. Portanto, é necessário que o T1CKI tenha um período de pelo menos 4 Tosc (e um pequeno delay de 40ns do RC) dividido pelo valor do pré-scaler. O único requisito para os tempos do T1CKI alto e baixo é que eles não ultrapassem o limite mínimo de amplitude de pulsação de 10ns. Consulte as especificações elétricas apropriadas na Tabela 17.8, parâmetros 45, 46 e 47,

FIGURA 7.1: DIAGRAMA DE BLOCOS DO TIMER1

7.3 Operação do Timer1 no Modo Contador Assíncrono

Se o bit de controle T1SYNC (T1CON<2>) estiver ativado, a entrada do clock externo não está sincronizada. O temporizador continua a incrementar de forma assíncrona aos clocks de fase internos. O temporizador continuará a funcionar durante a Hibernação e pode gerar uma interrução no overflow, a qual acordará o processador. Sendo assim, precauções específicas com o software são necessárias para ler/ escrever no temporizador (Seção 7.3.2 "Ler e Escrever no Timer1 no Modo Contador Assíncrono").

Nota:

No modo Contador Assíncrono, o Timer1 não pode ser utilizado como uma base de tempo para operações de captura e comparação.

7.3.1 TEMPORIZAÇÃO DA ENTRADA DO CLOCK EXTERNO COM O CLOCK NÃO-SINCRONIZADO

Se o bit de controle T1SYNC está ativado, o temporizador incrementará de forma completamente assíncrona. A entrada do clock deverá atender a certos requisitos mínimos de tempo alto e baixo. Consulte a Tabela 17.8 na Seção de Especificações Elétricas, parâmetros de temporização 45, 46 e 47.

A leitura dos registradores TMR1H ou TMR1L enquanto o temporizador está funcionando por meio de um clock externo assíncrono será válida (tomando-se cuidado com isso no hardware). Entretanto, o usuário deverá ter em mente que a leitura de um temporizador de 16 bits em dois valores de 8 bits cria certos problemas, pois o temporizador pode sofrer overflow entre as leituras.

Para escritas, é recomendado que o usuário simplesmente pare o temporizador e escreva os valores desejados. Uma contenção da escrita pode ocorrer devido à gravação nos registradores do temporizador enquanto o registrador está incrementando. Isto pode produzir um valor imprevisível no registrador do temporizador.

A leitura do valor de 16 bits requer algum cuidado. O Exemplo 7.1 é um exemplo de rotina para ler o valor do temporizador de 16 bits. Ele é útil no caso de o temporizador não poder ser parado.

; Todas as interrupções estão desabilitadas

MOVF TMR1H, W ;Lê o byte alto

MOVWF TMPH

MOVF TMR1L, W ;Lê o byte baixo

MOVWF TMPL

MOVF TMR1H, W ;Lê o byte alto

SUBWF TMPH, W ;Subtrai a primeira leitura

;da segunda

BTFSC STATUS,Z ;Se o resultado = 0

GOTO CONTINUE ;Bom. 16-bit lidos

;

; TMR1L pode ter sofrido overflow entre a leitura dos bytes

; alto e baixo. Lendo novamente os bytes alto e baixo obterá

; agora o valor correto

;

MOVF TMR1H, W ;Lê o byte alto

MOVWF TMPH

MOVF TMR1L, W ;Lê o byte baixo

MOVWF TMPL

;Reabilitar as interrupções (se necessário)

CONTINUE ;Continue com seu código

7.4 Oscilador do Timer1

Um circuito de oscilador de cristal é construído entre os pinos T1OSI (entrada) e T1OSO (saída do amplificador). Ele é habilitado ativando-se o bit de controle T1OSCEN (T1CON<3>). Ele continuará a funcionar durante a Hibernação. Ele é, a princípio indicado para um cristal de clock de 32,768 kHz. A Tabela 7.1 apresenta a seleção do capacitor para o oscilador do Timer1.

O usuário deve prover um delay no tempo do software a fim de assegurar o start-up apropriado do oscilador.

|

Freq |

C1 |

C2 |

|

32,768 kHz |

15 pF |

15 pF |

Nota: Estes valores são somente para orientação de projeto. Consulte a Nota de Aplicação AN826 "Princípios Básicos dos Osciladores de Cristal e Seleção do Cristal para Dispositivos rfPIC® e PIC®" (DS00826) para maiores informações sobre a Seleção do Cristal/ Capacitor.

7.5 Reinicializando o Timer1 com a Utilização de uma Saída Trigger do CCP

Se o módulo CCP1 está configurado no modo Comparação para gerar um "disparador (trigger) de evento especial" (CCP1M<3:0> = 1001), este sinal irá reinicializar o Timer1.

Nota:

Os triggers de evento especial do módulo CCP1 não ativarão o bit de sinalização de interrupção TMR1IF (PIR1<0>).

O Timer1 deve estar configurado para o modo temporizador ou o modo Contador Sincronizado para usufruir da vantagem desta propriedade. Se o Timer1 estiver funcionando no modo Contador Assíncrono, esta operação de Reinicialização pode não funcionar.

No caso de uma escrita no Timer1 coincidir com um trigger de evento especial do CCP1, prevalecerá a escrita.

Neste modo de operação, o par de registradores CCPRxH:CCPRxL se torna efetivamente o registrador de período para o Timer1.

7.6 Reinicializando o Par de Registradores do Timer1 (TMR1H, TMR1L)

Os registradores TMR1H e TMR1L não são reinicializados para 00h em uma POR ou em nenhuma outra reinicialização, exceto pelos triggers (disparadores) de evento especial do CCP1 (veja a Seção 9.2.4 "Trigger de Evento Especial").

O registrador T1CON é reinicializado para 00h em uma Reinicialização de Power-On ou em uma Reinicialização de Brown-Out, as quais desligam o temporizador e deixam uma pré-escala de 1:1. Em outras Reinicializações, o registrador não é afetado.

7.7 Pré-scaler do Timer1

O contador do pré-scaler é apagado em escritas nos registradores TMR1H ou TMR1L.

TABELA 7.2: REGISTRADORES ASSOCIADOS AO TIMER1 COMO TEMPORIZADOR/ CONTADOR

|

Endereço |

Nome |

Bit 7 |

Bit 6 |

Bit 5 |

Bit 4 |

Bit 3 |

Bit 2 |

Bit 1 |

Bit 0 |

Valor na POR |

Valor em Todas as Outras Reinicializações |

|

0Bh, 8Bh, 10Bh, 18Bh |

INTCON |

GIE |

PEIE |

T0IE |

INTE |

RBIE |

T0IF |

INTF |

RBIF |

0000 000x |

0000 000u |

|

0Ch |

PIR1 |

EEIF |

CMIF |

RCIF |

TXIF |

--- |

CCP1IF |

TMR2IF |

TMR1IF |

0000 -000 |

0000 -000 |

|

8Ch |

PIE1 |

EEIE |

CM1IE |

RCIE |

TXIE |

--- |

CCP1IE |

TMR2IE |

TMR1IE |

0000 -000 |

0000 -000 |

|

0Eh |

TMR1L |

Holding Register para o Byte Menos Significativo do Registrador TMR1 de 16 bits |

xxxx xxxx |

uuuu uuuu |

|

0Fh |

TMR1H |

Holding Register para o Byte Mais Significativo do Registrador TMR1 de 16 bits |

xxxx xxxx |

uuuu uuuu |

|

10h |

T1CON |

--- |

--- |

T1CKPS1 |

T1CKPS0 |

T1OSCEN |

T1SYNC |

TMR1CS |

TMR1ON |

--00 0000 |

--uuuu |

Legenda:

x = desconhecido

u = inalterado

- = não implementado, lido como "0"

células sombreadas = não utilizadas pelo módulo Timer1